Introduction: The Next Memory Revolution?

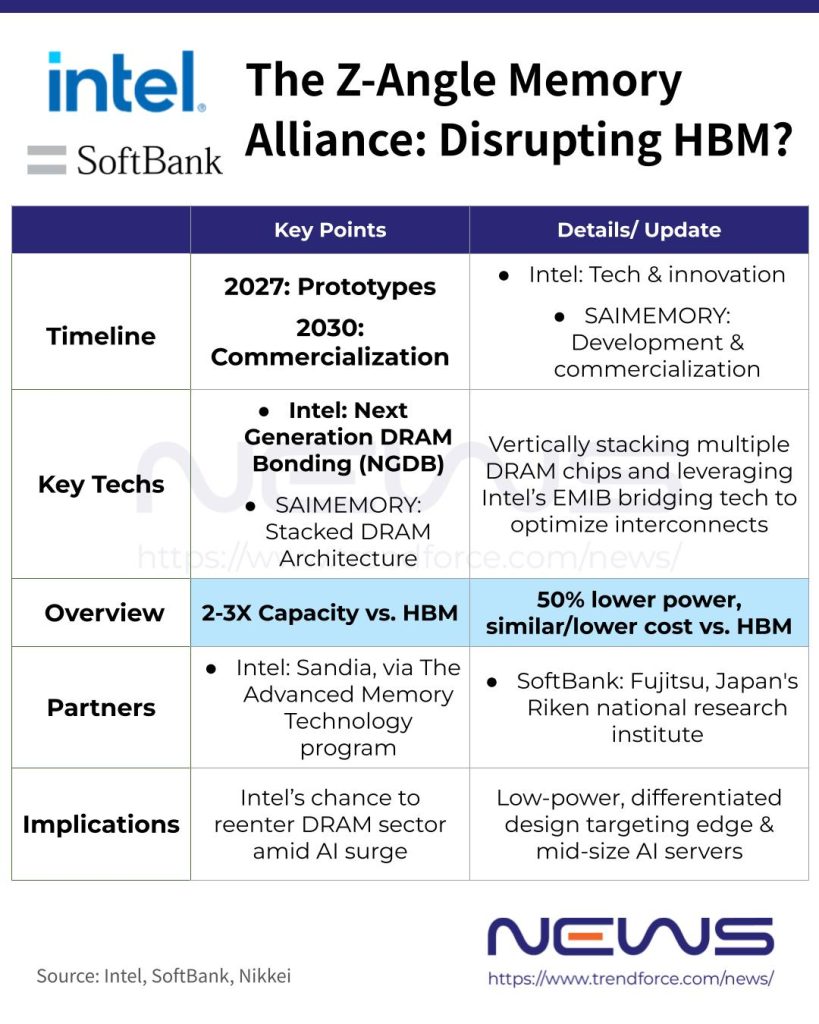

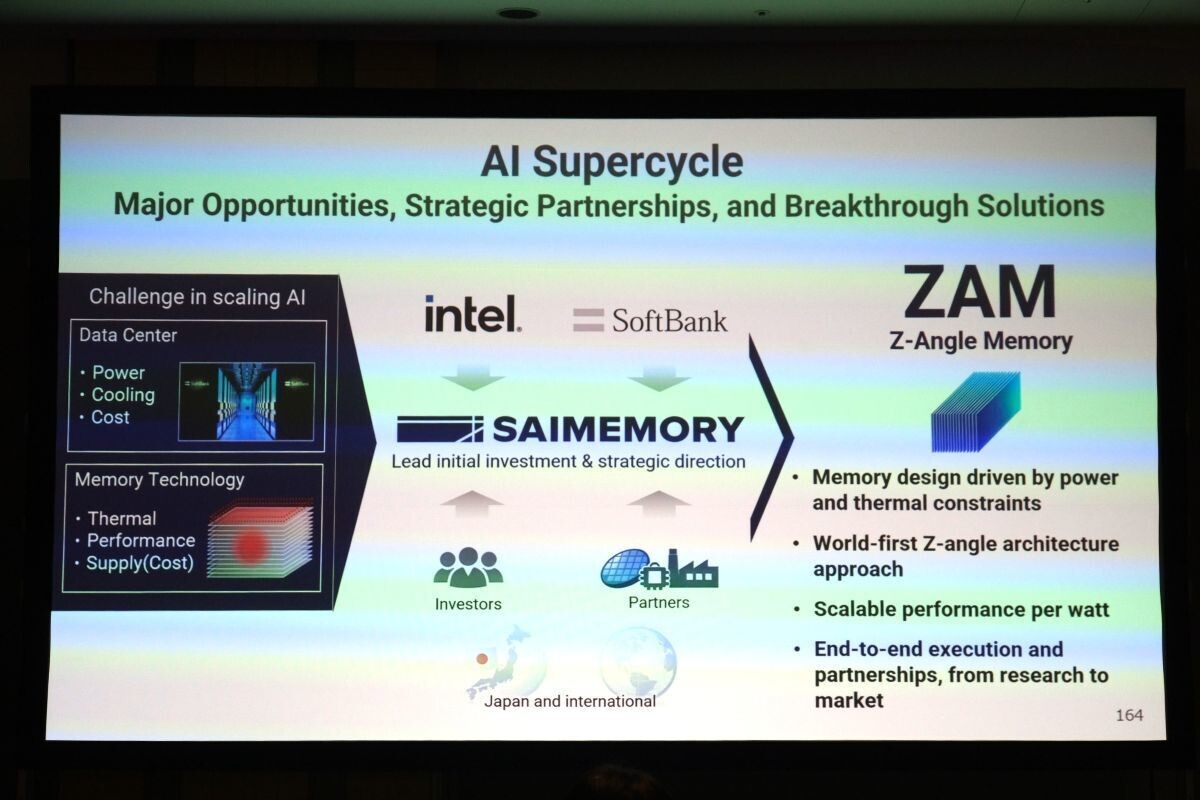

The semiconductor industry rarely stands still, and the race for high-bandwidth memory (HBM) represents one of the most consequential battlegrounds for artificial intelligence infrastructure. In late 2024, Intel and Soft Bank-backed Saimemory announced an ambitious partnership to develop Z-Angle Memory, a novel stacked DRAM architecture designed to challenge the dominant positions of Samsung and SK Hynix in the HBM market. This collaboration signals a fundamental shift in how major technology companies are approaching memory architecture for AI workloads, with prototypes expected by 2028 and commercial availability targeted for 2029.

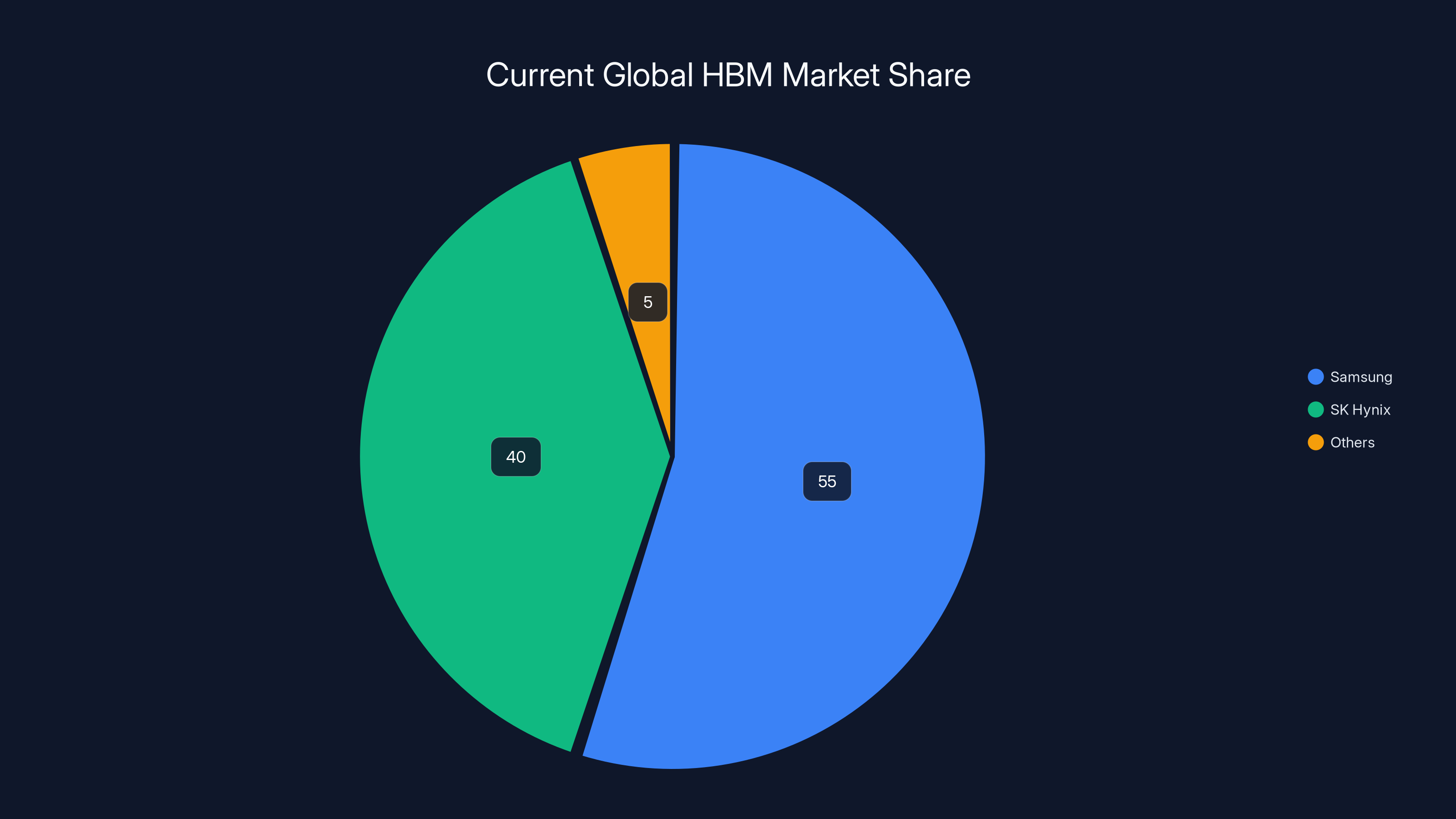

What makes this announcement particularly significant is the strategic timing and the technological ambition behind it. While HBM technology has become essential for training and running large language models, the current market is heavily concentrated. Samsung and SK Hynix control approximately 95% of the global HBM market, creating both supply constraints and pricing pressures for cloud service providers and AI companies. Intel's re-entry into advanced DRAM development after decades of absence represents a major strategic pivot, while Soft Bank's investment reflects Japan's broader effort to rebuild domestic semiconductor capabilities and reduce dependency on South Korean memory manufacturers.

However, the announcement also carries echoes of previous technological ambitions that failed to materialize as expected. Intel's Optane and 3D XPoint initiatives were hyped as transformative memory technologies that would revolutionize data center performance, yet they ultimately resulted in hundreds of millions of dollars in write-offs and market disappointment. Micron similarly suffered significant losses from failed memory architecture experiments. This historical context creates legitimate skepticism about whether Z-Angle Memory will succeed where previous disruptive technologies stumbled, or whether it represents a more pragmatic and achievable evolution in memory architecture.

This comprehensive guide examines the Z-Angle Memory initiative from multiple angles: the technical specifications and claimed advantages, the competitive landscape dominated by Samsung and SK Hynix, the timeline and development challenges, the strategic motivations of Intel and Soft Bank, the historical precedents both encouraging and cautionary, and ultimately what success or failure would mean for the AI infrastructure industry and technology developers worldwide.

Understanding Z-Angle Memory: Technical Foundation

What Is Z-Angle Memory?

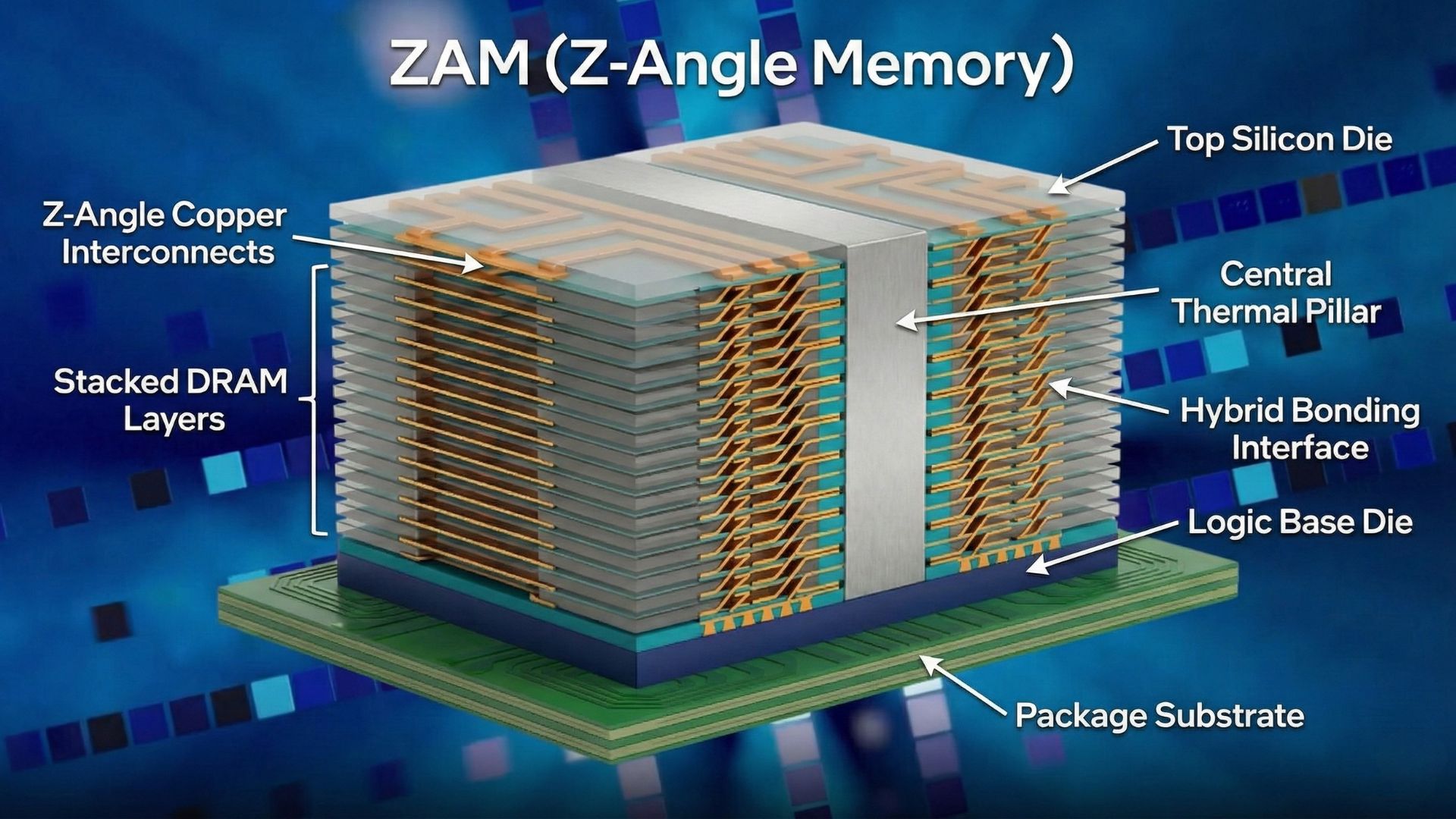

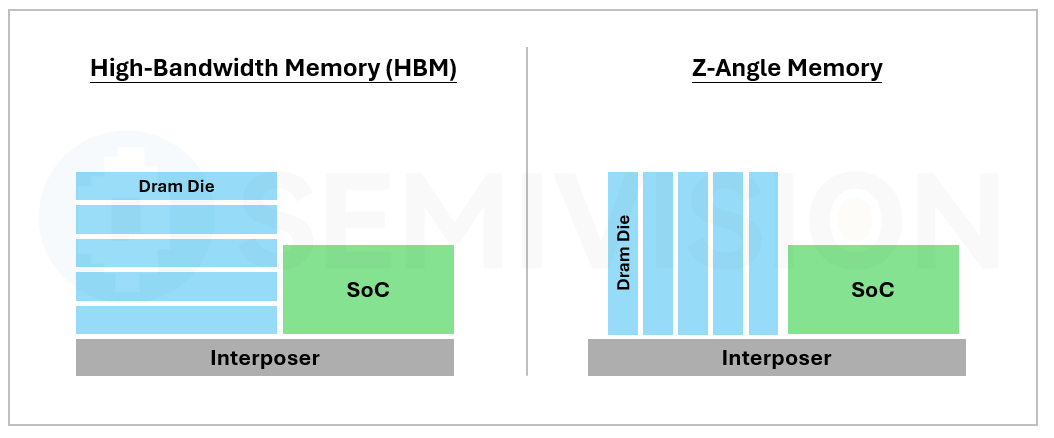

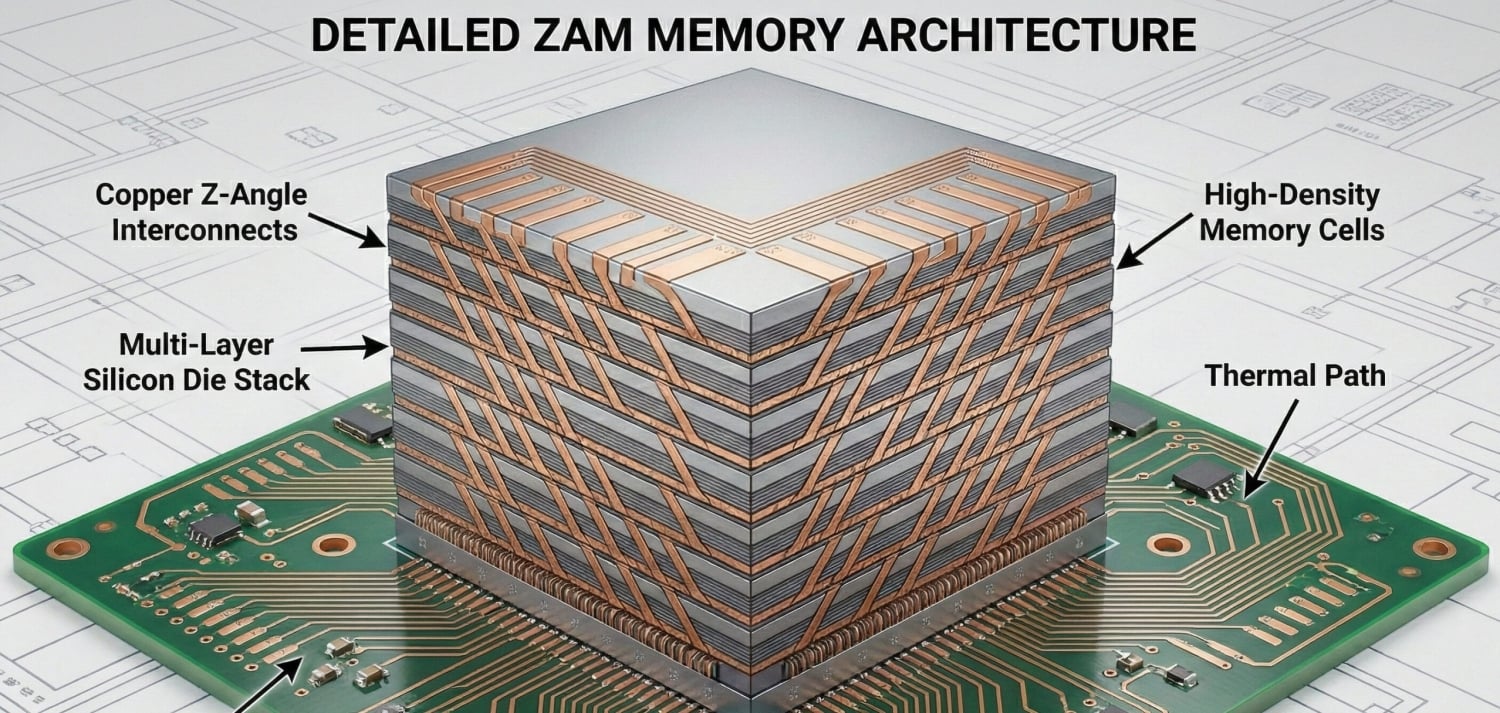

Z-Angle Memory represents a fundamental reimagining of how DRAM cells are physically stacked and interconnected within a memory package. Unlike traditional planar DRAM designs where cells are arranged horizontally across a single silicon die, or conventional vertical stacking approaches, Z-Angle Memory allegedly uses a tilted or diagonal configuration for the memory cells and their interconnecting pathways. The name itself—"Z-Angle"—suggests this three-dimensional orientation, where cells are accessed at angles rather than purely vertically or horizontally.

The technology builds on Intel's earlier Next Generation DRAM Bonding research, which was conducted under US-backed research programs exploring multi-layer DRAM stacking. This prior work provided a foundation for understanding how to bond multiple DRAM dies together while maintaining signal integrity and minimizing power loss. Z-Angle Memory takes this foundation and adds a geometric optimization layer, potentially reducing the signal path lengths and improving the efficiency of data movement within the stack.

From a physical perspective, Z-Angle Memory packages would likely contain multiple DRAM dies—potentially 8, 12, or even more layers—stacked vertically using micro-bumps or other bonding technologies. The innovation appears to center on how these layers are electrically connected and how data routes through the stack, with the angled approach potentially offering advantages in terms of reduced latency, improved bandwidth, and lower power consumption compared to existing HBM3 and future HBM4 designs.

How Z-Angle Memory Differs From Current HBM

Current high-bandwidth memory, primarily HBM3 and the upcoming HBM3e standards developed by SK Hynix and Samsung, uses a vertical stacking approach with through-silicon vias (TSVs) that connect the memory dies. These TSVs are essentially tiny vertical copper channels that allow signals to pass through the silicon wafers. While this approach has proven effective, it comes with fundamental physical constraints: the longer the signal path, the more power is required to transmit data, and the greater the potential for signal degradation.

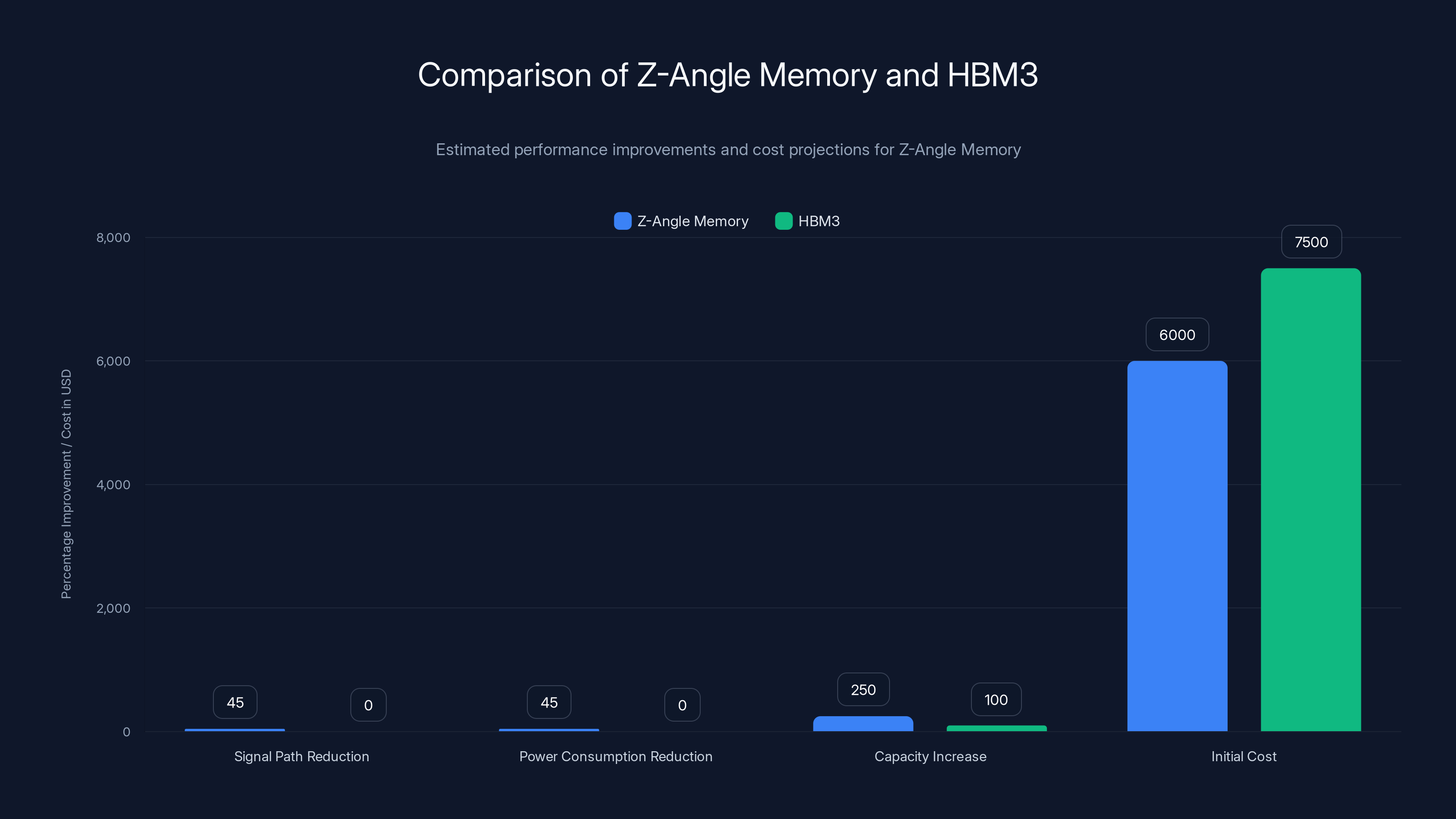

Z-Angle Memory potentially addresses these constraints through its geometric optimization. By angling the memory cells and their interconnects, the technology might reduce the effective distance signals must travel within the stack, thereby reducing capacitance and the associated power consumption. This geometric optimization could explain the claimed 40-50% reduction in power consumption compared to current HBM designs.

Additionally, the claimed 2-3x increase in capacity suggests that Z-Angle Memory can achieve higher memory densities within the same physical footprint. This could result from more efficient use of the silicon area within each layer or from enabling additional layers within a practical physical package size. Higher density directly translates to more memory bandwidth for AI workloads, as HBM capacity and bandwidth are closely linked through the bus width and clock frequencies.

The Physics of Stacked Memory Architecture

Understanding why stacked memory matters requires examining the fundamental physics of data movement. When a processor requests data from memory, that request must travel from the CPU to the memory controller, then to the memory package itself. The data must then traverse through multiple layers of the memory hierarchy before reaching the requested DRAM cell. Every millimeter of distance the signal travels requires energy and introduces propagation delay.

In current HBM designs, the signal paths follow relatively straightforward vertical routes. With Z-Angle Memory's angled geometry, the signal paths could be optimized to follow the shortest possible distance through the three-dimensional space of the stack. This optimization is analogous to finding the shortest path through a three-dimensional maze rather than being constrained to vertical corridors.

The power savings would come from reduced capacitance in the signal lines. Shorter, optimized pathways have lower total capacitance, and since power consumption in digital circuits is proportional to

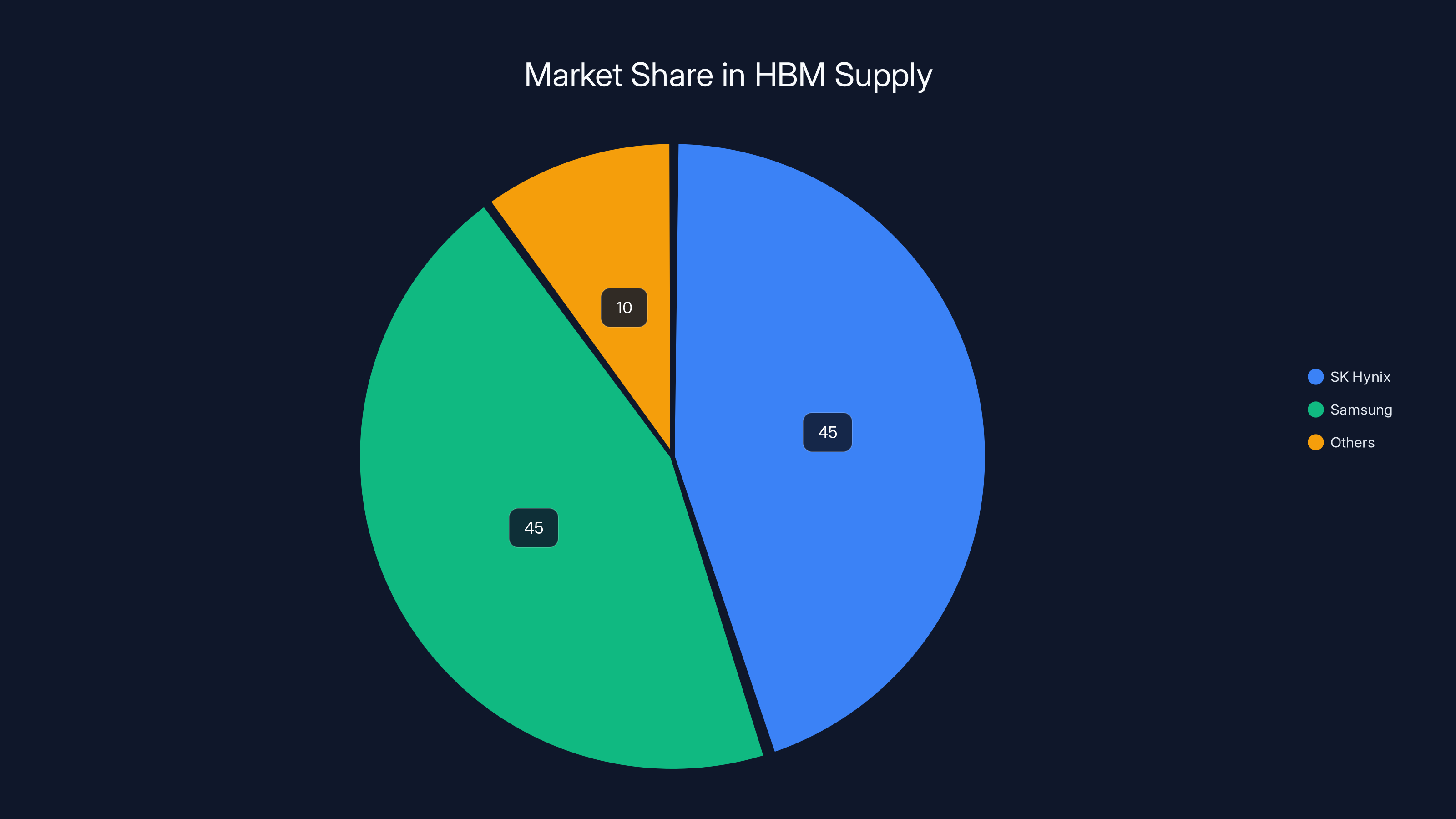

SK Hynix and Samsung dominate the HBM market, each holding an estimated 45% share, leaving only 10% for other suppliers. Estimated data.

The Current HBM Market: Dominance and Constraints

Market Concentration and Supply Dynamics

The high-bandwidth memory market represents one of the most concentrated segments in semiconductors, with SK Hynix and Samsung controlling the vast majority of global supply. This concentration has created a critical bottleneck for AI infrastructure development. As companies like Meta, Open AI, Google, Microsoft, and others deploy increasingly large language models, their demand for HBM has grown exponentially, far outpacing supply growth.

In 2023 and early 2024, HBM shortage became a constraint on data center deployments. Companies were unable to source sufficient HBM to build out their GPU clusters for AI training and inference at the pace they desired. NVIDIA's highly anticipated H100 and H200 GPUs, which rely heavily on HBM for their performance characteristics, faced allocation constraints. This supply limitation created opportunities for Samsung and SK Hynix to command premium pricing while negotiating favorable long-term contracts with major cloud providers.

The market dynamics have created a situation where a handful of manufacturers essentially hold veto power over the pace of AI infrastructure expansion. This concentration of power is unprecedented in recent semiconductor history and has attracted the attention of governments, including the US and Japanese administrations, both of which view semiconductor supply chain independence as a strategic priority.

Performance Specifications of Current HBM Standards

To understand what Z-Angle Memory must achieve to be competitive, examining current HBM specifications is essential. HBM3, the current mainstream standard, provides memory stacks with up to 141 GB/s of bandwidth per stack with typical configurations of 24 GB capacity. HBM3e, introduced in 2024, increases bandwidth to approximately 200+ GB/s per stack and capacity to 36 GB, representing a significant generational improvement.

These specifications are achieved through aggressive engineering: HBM3 uses 12 layers of DRAM dies, each connected via through-silicon vias with pitches as small as 20 micrometers. The operating frequency reaches 819 MHz, and the voltage is optimized through power management techniques. The bandwidth-per-watt metric has become increasingly important, as data center operators must balance performance gains against cooling and power infrastructure costs.

Z-Angle Memory's claimed specifications—2-3x capacity improvement and 40-50% power reduction—would theoretically position it ahead of HBM3e. If achieved, a Z-Angle Memory stack with 72 GB capacity and HBM3e-equivalent bandwidth but consuming significantly less power would be extraordinarily attractive. However, the gap between claimed specifications and commercial reality is vast, as the history of memory technology demonstrates repeatedly.

Pricing and Cost Structures

HBM pricing represents a critical factor in AI infrastructure costs. Current HBM3 memory costs approximately $5,000-8,000 per stack in volume, representing roughly 10-20% of total GPU platform costs. For large-scale data centers deploying thousands of GPUs, HBM costs accumulate into millions or billions of dollars. A 40% reduction in power consumption would translate directly into operational savings, as cooling and power delivery represent 20-40% of data center operating expenses in AI-heavy facilities.

Z-Angle Memory's introduction could disrupt pricing dynamics if manufactured at scale. A new competitor offering comparable or superior performance while using less power could pressure Samsung and SK Hynix to improve their own roadmaps or reduce pricing. Historically, memory market entries by new players have been rare and difficult; when they do occur, they typically take years to reach meaningful volume production and market share.

Z-Angle Memory is projected to reduce signal paths and power consumption by approximately 45% and increase capacity by 2-3 times compared to HBM3, with initial costs estimated to be competitive at around $6,000 per stack. (Estimated data)

Intel's Strategic Motivation and Memory Resurrection

The Departure From DRAM and Return To Advanced Memory

Intel's participation in this venture represents a remarkable strategic reversal. The company exited the DRAM market in the mid-1980s to focus on microprocessors, a decision that proved commercially successful for decades. The DRAM business is capital-intensive, cyclical, and offers lower profit margins than specialty products like high-performance processors or specialty memory. Returning to advanced memory is not a casual decision for Intel's leadership; it reflects deep strategic concerns about data center competitiveness in the AI era.

The motivation for Intel's re-entry becomes clear when examining the architecture of AI systems. Modern AI accelerators—whether NVIDIA GPUs, Google TPUs, or AMD MI300 series—are fundamentally memory-limited. The compute capability of processors has grown exponentially following Moore's Law trends, but memory bandwidth has not kept pace. This creates a bottleneck where processors sit idle waiting for data to arrive from memory. HBM partially addresses this bottleneck by providing high bandwidth, but it does not fully solve the memory wall problem.

Intel's participation in Z-Angle Memory development positions the company at the forefront of addressing this architectural constraint. Additionally, Intel operates foundry services through Intel Foundry Services (IFS), competing with TSMC and Samsung. If Intel could manufacture advanced memory products in its own fabs, it would enhance the attractiveness of Intel's foundry offerings and create vertical integration advantages similar to Samsung's integrated memory-and-logic strategy.

Technology Transfer and Intellectual Property

Intel's contribution to the partnership appears to be primarily technological rather than financial. According to reports, Intel is providing technology derived from its Next Generation DRAM Bonding research, which benefited from US government funding and represented significant intellectual property development. This technology transfer is strategically valuable because it accelerates Saimemory's development timeline and provides access to Intel's expertise in advanced packaging and bonding technologies.

The intellectual property arrangement also reflects pragmatic considerations. Intel could theoretically pursue Z-Angle Memory development independently, but partnering with Soft Bank provides several advantages: it reduces Intel's financial risk, provides access to Japanese manufacturing expertise, and creates a pathway for potential manufacturing in both the US (through Intel fabs) and Japan (through local partners). For Soft Bank, accessing Intel's technology accelerates development and provides legitimacy from a globally recognized semiconductor company.

Foundry Strategy and Vertical Integration

Intel's broader foundry ambitions inform its participation in Z-Angle Memory. Intel has invested heavily in new manufacturing facilities in the US, Arizona, Germany, Ireland, and other locations. These fabs are built to support advanced process nodes and specialty products. If Z-Angle Memory proves successful, Intel could potentially manufacture these memory products in its fabs, creating a vertically integrated offering: Intel designs advanced memory, manufactures it, and sells it to system designers and platform companies.

This vertical integration would differentiate Intel's foundry services from pure-play foundries like TSMC. It would allow Intel to offer customers integrated solutions combining processors, memory, and other components optimized for specific workloads. In an era where system-level design matters increasingly, such integration capabilities could be valuable to cloud providers and AI infrastructure companies.

Soft Bank's Strategic Objectives and Japanese Semiconductor Ambitions

Rebuilding Japan's Memory Leadership Position

Soft Bank's investment in Z-Angle Memory through Saimemory reflects broader Japanese government and corporate concerns about semiconductor competitiveness. Japan once dominated DRAM manufacturing during the 1980s and 1990s, with companies like NEC, Mitsubishi, and Hitachi controlling significant global market share. Over subsequent decades, this position eroded as South Korean competitors (Samsung and SK Hynix) invested more aggressively in manufacturing scale and process improvements, while Japanese companies consolidated or exited the DRAM business.

The 3 billion yen (approximately $19-20 million) investment that Soft Bank is providing during the prototype phase is substantial relative to typical R&D spending for memory technology, but modest relative to the capital requirements for high-volume memory manufacturing. This suggests the partnership is structured with expectations for significantly larger investments during later development phases. Japanese government support through mechanisms like the Green Innovation Fund and other programs could provide additional capital.

From Soft Bank's perspective, success in Z-Angle Memory would position the company as a leader in next-generation memory technology and potentially as a foundational technology provider for Japanese semiconductor resurgence. Soft Bank's Arm Holdings subsidiary already plays a critical role in semiconductor architecture through instruction set licensing; adding memory technology expertise would enhance Soft Bank's influence in the semiconductor ecosystem.

Supply Chain Diversification and Economic Security

Japanese policymakers are deeply concerned about reliance on South Korean memory suppliers. The COVID-19 pandemic and subsequent supply chain disruptions highlighted vulnerabilities in semiconductor supply chains. Having domestically developed and manufactured advanced memory would provide strategic autonomy and reduce geopolitical risks associated with supply disruptions.

From an economic perspective, memory manufacturing represents significant employment and industrial activity. Japan's manufacturing sector has faced decades of pressure from lower-cost competitors in China and other Asian countries. Re-establishing memory manufacturing capability would provide high-value industrial activity and support Japanese technological leadership in critical infrastructure sectors.

Investment Thesis and Timeline

Soft Bank's investment thesis appears to be grounded in pragmatic expectations about market timing. By 2029, when Z-Angle Memory is targeted for commercial availability, the HBM market is expected to be substantially larger than today, driven by continued AI infrastructure expansion. The addressable market for advanced memory in AI data centers alone could reach hundreds of billions of dollars by 2029, providing significant opportunities for a viable memory competitor.

The timeline also allows for realistic development and manufacturing ramp-up. Prototype development from 2024-2028 provides years for iterative improvement, yield optimization, and addressing technical challenges. Commercial availability in 2029 allows another 1-2 years for initial production and customer qualification before major volume ramps. This extended timeline, while lengthy, is actually realistic for memory technology given the manufacturing complexity and qualification requirements for AI platforms.

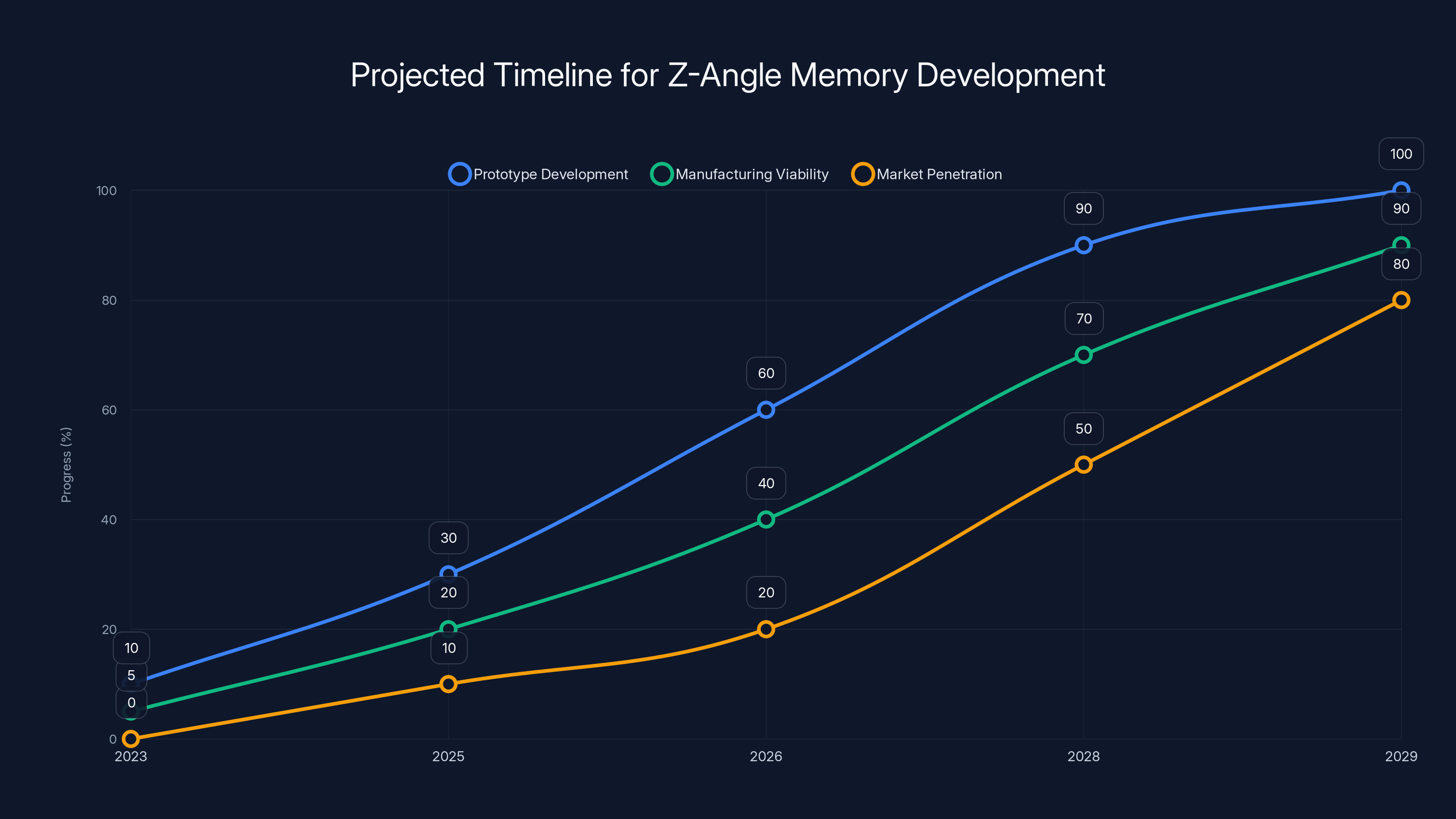

The timeline suggests prototype development could reach 100% by 2029, with manufacturing viability and market penetration following closely if no major obstacles arise. Estimated data.

Competitive Analysis: Samsung, SK Hynix, and Others

Samsung's HBM Strategy and Roadmap

Samsung has positioned itself as the premium HBM provider, with aggressive roadmap commitments. The company has been developing HBM3e with advanced features and planning HBM4 products for the 2025-2026 timeframe. Samsung's strategy emphasizes yield optimization, production scale, and continuous technical advancement. The company is investing billions in memory manufacturing facilities and research development.

Samsung's advantages are formidable: decades of DRAM manufacturing expertise, proven quality and reliability in high-end products, existing relationships with major customers, and manufacturing capacity. Samsung can leverage its existing memory fabs to produce HBM with relatively lower incremental capital compared to a new entrant. Additionally, Samsung produces memory for diverse applications (consumer, enterprise, mobile), allowing it to amortize R&D costs across larger volume.

Samsung's potential vulnerability is complacency. The company may not anticipate Z-Angle Memory as a credible threat through 2029, potentially reducing urgency in response. However, Samsung's management is sophisticated and aware of competitive threats; it is more likely to view Z-Angle Memory as a longer-term strategic challenge to address through roadmap acceleration or, if appropriate, through acquisition of the technology or the company developing it.

SK Hynix's Competitive Position

SK Hynix, Samsung's primary competitor, has focused on differentiation through specialized products and higher-margin applications. The company is known for aggressive cost optimization and manufacturing efficiency. SK Hynix has publicly committed to HBM3e production and advanced packaging innovations.

Like Samsung, SK Hynix benefits from established manufacturing capabilities and customer relationships. The company is likely to view Z-Angle Memory development as a signal to accelerate its own technology roadmap, ensuring that by 2029, HBM4 or equivalent products are available and proven. SK Hynix has demonstrated ability to move quickly when threatened by competitive developments, as evidenced by its rapid adoption of new process technologies and manufacturing techniques.

Emerging Competitors and Alternative Approaches

Beyond Samsung and SK Hynix, several other companies are exploring memory technologies that could impact HBM markets. Kioxia (formerly Toshiba's memory division) has researched 3D DRAM approaches, though these are still in early development phases. Micron has less focus on HBM specifically but maintains memory technology expertise. YMTC (a Chinese state-backed memory company) is investing heavily in advanced memory but currently lags in HBM performance.

These emerging competitors could benefit from Z-Angle Memory's development. If the technology proves successful, it could become an industry standard or inspire similar approaches. Alternatively, if Z-Angle Memory stumbles, it might discourage other new entrants and reinforce Samsung and SK Hynix's dominance.

Technology Differentiation Opportunities

The memory market has historically driven differentiation through process node advances (smaller transistor sizes), voltage and current optimizations, and packaging innovations. Z-Angle Memory's angled architecture represents a differentiation approach distinct from these traditional vectors. If successful, it could become a valuable portfolio item that the company can license to others or use for competitive advantage.

Competitors could respond by developing competing geometric optimizations, investing in alternative stacking approaches, or focusing on other performance metrics where they have advantages. The industry response to Z-Angle Memory will largely depend on initial technical validation and early customer feedback.

Technical Challenges and Development Risks

Manufacturing and Yield Complexities

Moving from prototype to commercial production in advanced memory is extraordinarily challenging. Memory manufacturing requires class-1 cleanrooms (fewer than one particle larger than 0.5 micrometers per cubic foot), precision equipment capable of patterning features smaller than 10 nanometers, and sophisticated process control systems. The manufacturing process for HBM involves hundreds of individual steps, each of which must be optimized for yield and quality.

Z-Angle Memory's angled architecture may introduce new manufacturing challenges. Creating perfectly aligned diagonal interconnects, maintaining electrical properties through complex three-dimensional structures, and bonding multiple layers while maintaining signal integrity are all areas where yield could suffer initially. The difference between a prototype that functions and a production process that achieves 70-80% yield is immense, often requiring 2-3 years of refinement.

History provides cautionary examples. Intel's 3D XPoint memory, which promised revolutionary performance and capacity, was ultimately abandoned due to manufacturing challenges and yield limitations that proved difficult to overcome. Yield problems converted what was technologically impressive into economically impractical, contributing to hundreds of millions in losses.

Thermal Management and Power Delivery

While Z-Angle Memory claims 40-50% power reduction, actual power consumption in early prototypes often exceeds projections. Advanced stacked memory systems generate significant heat in a small physical volume. Removing heat from 12+ layers of DRAM stacked vertically requires sophisticated thermal design and may necessitate additional packaging innovations. The thermal interface between the memory stack and the surrounding substrate, and between individual layers, becomes critical.

Power delivery to stacked memory is another challenge. Multiple layers require power distribution networks that maintain precise voltage across all layers simultaneously. As layer count increases and current density rises, managing IR drop (voltage drop due to resistance in the power delivery network) becomes increasingly difficult. Poor power delivery quality can lead to timing violations, signal integrity problems, and reduced yield.

Signal Integrity and Electrical Performance

Z-Angle Memory's geometric optimization likely involves shorter, more complex signal paths through the memory stack. While shorter paths reduce capacitance and power, they may increase inductance or create crosstalk issues between adjacent signal lines. Managing signal integrity at the clock frequencies required for competitive bandwidth (likely 2-3 GHz for Z-Angle Memory) over three-dimensional structures with many layers is technically sophisticated.

Electrical simulation and validation of these complex three-dimensional structures requires advanced computer models and extensive physical validation. Any mismatch between simulations and actual hardware performance could necessitate significant redesigns, extending the development timeline.

Process Technology Dependencies

Z-Angle Memory's success depends on access to advanced process technologies for manufacturing DRAM cells and interconnects. DRAM cell design at current nodes (20-15 nanometers for cell technology) requires extreme ultraviolet (EUV) lithography or multiple patterning techniques. These process technologies are available only from a small number of fabs globally, primarily TSMC and Samsung.

If Saimemory plans to manufacture in Japanese fabs, accessing cutting-edge process technology becomes an additional challenge. Japanese fab capabilities have declined relative to TSMC and Samsung. Building domestic EUV lithography capability or implementing next-generation patterning techniques in Japanese fabs would require substantial investment and could delay time-to-market.

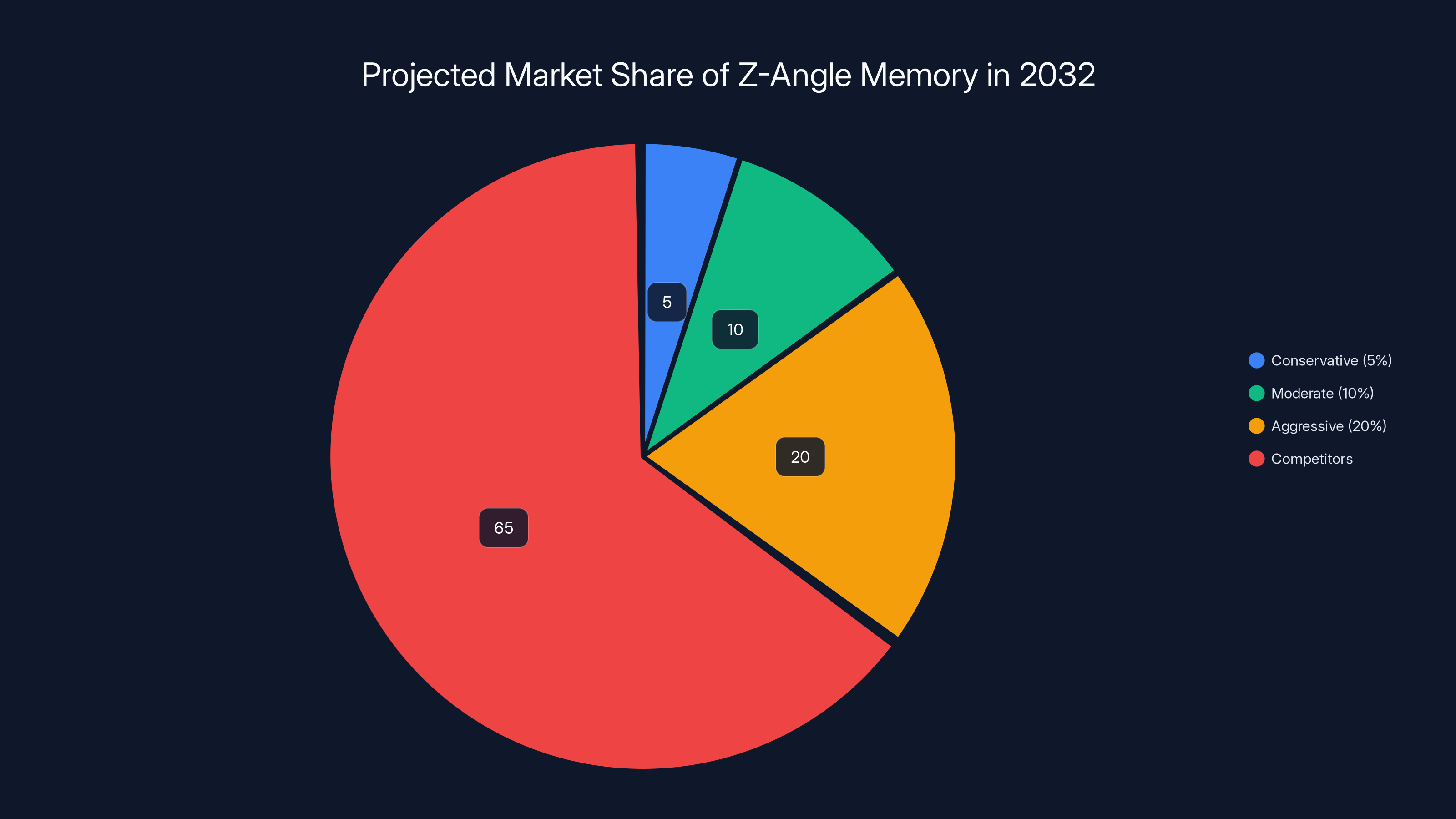

Estimated data: Z-Angle Memory's market share in 2032 could range from 5% to 20%, depending on pricing strategy and competitive dynamics.

Timeline and Commercialization Roadmap

Prototype Development (2024-2028)

The planned prototype phase extends approximately four years from the partnership announcement through early 2028. This timeline is actually compressed compared to typical memory technology development programs. During this phase, Saimemory and Intel researchers need to:

- Complete detailed engineering design of the Z-Angle architecture

- Conduct extensive circuit simulation and physical design

- Develop manufacturing process flows and optimization procedures

- Build and test initial prototype samples

- Validate electrical performance and power characteristics

- Address yield issues and optimize manufacturing

- Develop thermal management solutions

- Begin qualification testing for reliability and longevity

Successful prototype demonstration would require functional samples meeting or exceeding performance targets. This is a substantial achievement but remains far from commercial viability. Prototypes often function but demonstrate power consumption, yield, or reliability issues that require significant additional development.

Initial Commercial Production (2028-2029)

The transition from prototype to limited commercial production in 2029 represents an aggressive timeline. This phase involves scaling up from research fabrication (typically producing tens or hundreds of units) to limited commercial production (thousands to tens of thousands of units). Achieving acceptable yields at commercial scale is notoriously difficult.

During this phase, Saimemory and partners would work with early customers on design-in and qualification. AI system manufacturers like NVIDIA, AMD, and others would need to evaluate Z-Angle Memory modules, integrate them into test systems, and validate compatibility with existing infrastructure. This qualification process typically requires 6-12 months and extensive testing.

Volume Ramp and Market Penetration (2029 onwards)

Assuming successful initial production, volume ramp would follow. Reaching 10-20% of total HBM market share would require producing millions of units annually by 2030-2031. This depends on multiple factors: successful yield improvement, manufacturing scaling, customer acceptance, and competitive response from Samsung and SK Hynix.

Market penetration would likely be gradual. Early adopters might be companies particularly interested in power efficiency or those with supply relationships favoring new entrants. Broader adoption would depend on demonstrated reliability and favorable cost-performance metrics compared to Samsung and SK Hynix products.

Risk Factors and Timeline Slippage

History suggests timeline optimism is common in memory technology announcements. Multiple factors could extend the development timeline: technical challenges in achieving power or capacity targets, manufacturing yield issues, supply chain constraints for equipment or materials, or competitive developments that necessitate design changes.

If Z-Angle Memory experiences delays similar to other advanced memory projects, commercial availability could shift from 2029 to 2030 or 2031. Even this extended timeline would be valuable if it eventually delivers on performance promises, but further delays beyond this window would risk the opportunity being overtaken by competing technologies.

Historical Precedents: Learning From Memory Technology Failures

Intel's Optane and 3D XPoint: A Cautionary Tale

Intel's Optane memory initiative, based on 3D XPoint technology, represents the most relevant historical precedent for Z-Angle Memory. Announced in 2015 with tremendous fanfare, Optane was positioned as revolutionary technology offering superior performance and capacity compared to traditional NAND flash or DRAM.

The initial appeal of Optane was substantial. 3D XPoint promised 10x higher density than conventional NAND flash while offering faster performance and better power efficiency. For data center applications, particularly caching and storage tiers, Optane seemed ideally positioned. Intel invested billions developing the technology, constructing manufacturing facilities, and bringing products to market.

However, Optane never achieved the commercial success envisioned. Several factors contributed to its failure: manufacturing yields remained lower than required for profitable operations, the price premium was difficult to justify given modest performance gains in real-world applications, the emergence of alternatives (improved NAND flash, advancing DRAM technologies) reduced the compelling use cases, and customer adoption remained limited.

By July 2022, Intel formally discontinued Optane, acknowledging the strategic misstep through a $559 million inventory write-off in its quarterly financial results. This loss reflected not just the immediate impact of shutting down a product line, but years of R&D investment, capital expenditures for manufacturing, and organizational effort that yielded no sustained business.

Micron's Memory Technology Struggles

Micron Technologies, through its acquisition of Elpida after that company's 2012 bankruptcy, inherited exposure to failed memory technology bets. Elpida, a Japanese DRAM manufacturer, had invested substantially in competing with Samsung and SK Hynix but ultimately lacked the capital and scale to sustain profitable operations. Micron absorbed these operations and refocused on specific niches, including non-volatile memory and specialized DRAM applications.

Micron's experience demonstrates the capital intensity and competitive brutality of the memory business. Even a technologically capable company with strong engineering talent (Elpida had this) could not compete against better-capitalized competitors with superior manufacturing scale. This lesson is particularly relevant for Saimemory, a company without the existing DRAM manufacturing infrastructure or global customer relationships of established players.

What Distinguishes Z-Angle Memory From Previous Failures

Z-Angle Memory does have some characteristics that differentiate it from Optane's unfortunate trajectory. First, the technology is positioned squarely within the existing HBM market rather than trying to create a new category. HBM demand is proven and growing; Z-Angle Memory is attempting to participate in this established market rather than inventing one.

Second, Z-Angle Memory benefits from partnership with Intel, a company with semiconductor credibility despite its Optane struggles. Intel's involvement in technology development and potential manufacturing access provides advantages that pure startups lack. Additionally, Soft Bank's financial backing, while not unlimited, provides substantially greater resources than many memory startups.

Third, Z-Angle Memory's claimed improvements (2-3x capacity, 40-50% power reduction) are more modest than Optane's claimed revolutionary advantages. More conservative claims are harder to miss and may be more achievable, though they also provide less compelling differentiation.

The Pattern of Memory Technology Disruptions

Historically, major disruptions in memory technology come from process node advances (moving from 40nm to 20nm to 10nm, etc.) or from fundamental architectural changes (moving from DDR3 to DDR4, introducing Fin FET transistors, implementing TSVs for stacking). These disruptions typically take 3-5 years from research through widespread adoption and are often driven by the leading manufacturers themselves.

New entrant manufacturers attempting to disrupt the memory market from outside the established player base have a historically poor success rate. Without existing manufacturing infrastructure, customer relationships, and manufacturing expertise, new entrants face nearly insurmountable competitive barriers. Successful memory companies maintain dominance through continuous incremental improvement and massive capital investment.

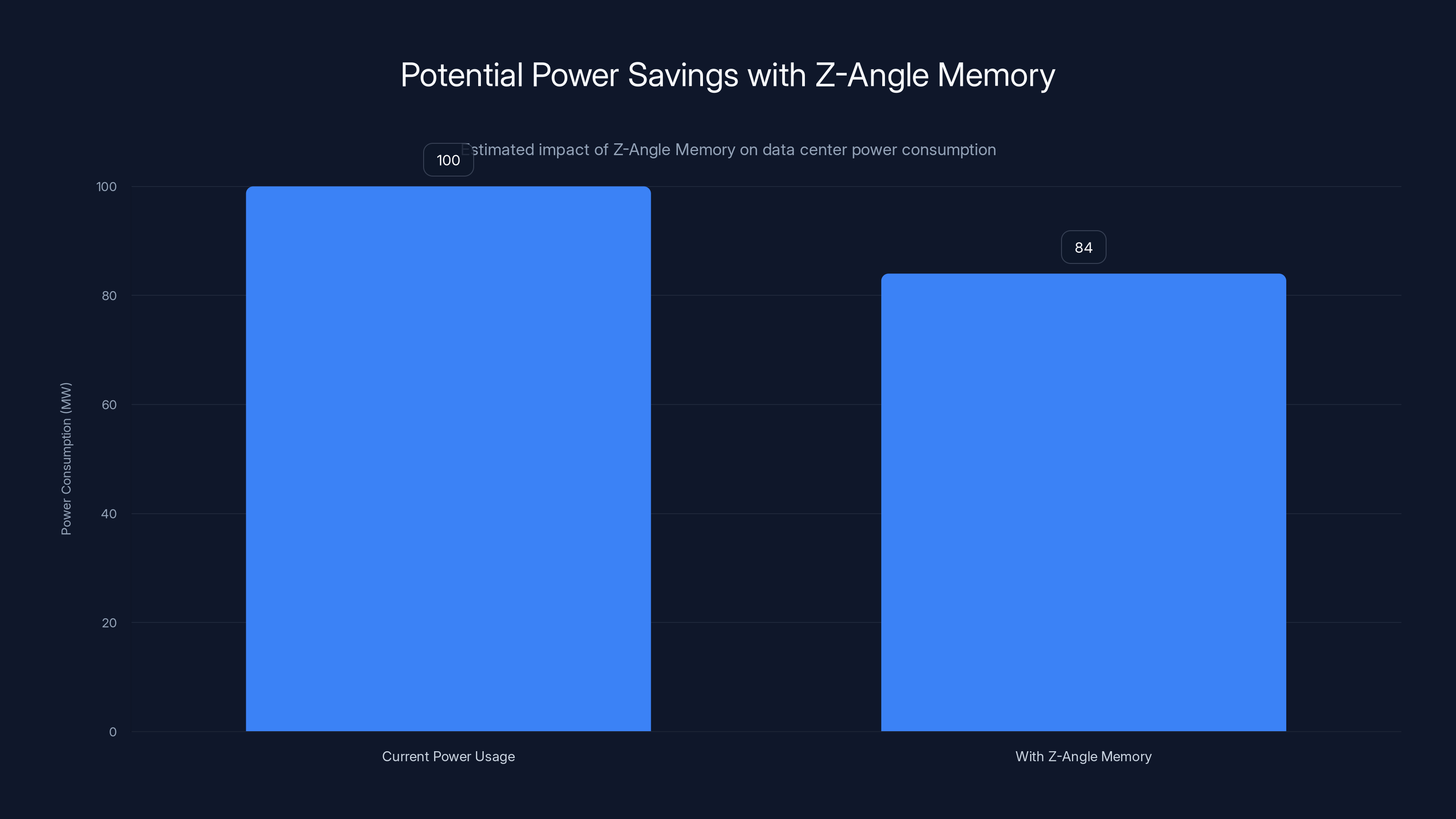

Implementing Z-Angle Memory could reduce data center power consumption by 12-16 MW, leading to significant cost savings. (Estimated data)

Impact on AI Infrastructure and Data Centers

Memory as the AI Bottleneck

Artificial intelligence workloads, particularly large language models and vision transformers, are fundamentally memory-bound rather than compute-bound. These workloads access memory frequently and in patterns that stress traditional memory hierarchies. The compute-to-memory bandwidth ratio in modern AI accelerators creates situations where the processor must wait for memory data more often than it can execute computations.

This memory bottleneck becomes increasingly severe as model sizes grow. A 70-billion-parameter language model requires accessing hundreds of gigabytes of weights and activations during inference. Even with high-bandwidth memory, feeding a GPU with sufficient data remains a fundamental architectural challenge. Z-Angle Memory's claimed 2-3x capacity improvement would directly address this bottleneck by allowing more model parameters and intermediate activations to reside in high-bandwidth memory closer to compute engines.

Power Efficiency in Data Centers

Data center power consumption has emerged as a critical constraint for AI infrastructure expansion. Large language model training and deployment consume massive amounts of electricity. A single data center running large-scale AI workloads can consume as much power as a small city. The associated cooling and electrical infrastructure costs are enormous.

Z-Angle Memory's claimed 40-50% power reduction in memory operations would translate into measurable data center cost savings. If a typical AI training run spends 30-40% of total power budget on memory operations and cooling, a 40% reduction in memory power could reduce total data center power by 12-16%. For a facility consuming 100 megawatts, this represents 12-16 megawatts of power savings, translating to approximately $10-15 million in annual electricity costs at typical data center rates.

These savings provide sufficient economic incentive for cloud providers to adopt Z-Angle Memory if performance and reliability match or exceed alternatives. The power efficiency advantage could be particularly compelling for providers operating in regions with high electricity costs or limited power availability.

Cost Implications and Infrastructure Budgeting

AI data center infrastructure budgeting involves substantial allocations for memory. Z-Angle Memory's potential cost competitiveness (if manufacturing achieves acceptable yields) could reduce total infrastructure costs. Additionally, higher capacity and efficiency could reduce the number of GPU systems required to deliver specific performance levels, with cascading cost implications across the entire facility.

For companies building multi-billion-dollar data centers for AI inference and training, memory cost reductions and efficiency gains compound across thousands of GPU systems. Even a 5-10% reduction in total cost of ownership could justify switching to Z-Angle Memory if risk is acceptable.

Regulatory and Geopolitical Considerations

US Government Support and Strategic Importance

Z-Angle Memory development benefits from US government policy supporting semiconductor independence and manufacturing. Programs like the CHIPS Act, which allocates $52 billion to semiconductor manufacturing and design, may provide funding or manufacturing support for advanced memory projects that strengthen US semiconductor capacity.

The US government views memory technology as strategically important. Chinese competition in semiconductor technology is a stated policy concern, and supporting diverse memory suppliers reduces reliance on a concentrated supply base dominated by South Korean companies. Intel's involvement in Z-Angle Memory development aligns with US policy objectives of maintaining semiconductor leadership and manufacturing capability.

Japanese Government Industrial Policy

Japan's government is actively promoting semiconductor resurgence through industrial policy initiatives. The Growth Strategy Initiative and Economic Security Promotion Act both support advanced memory development. Soft Bank's investment may be partially motivated by understanding Japanese government support mechanisms for semiconductor projects.

Japanese industrial policy historically has supported strategic industries through direct investment, preferential regulations, and manufacturing support. If Z-Angle Memory shows promise, Japanese government support could materially accelerate development timelines or provide manufacturing capacity access through Japanese fab partnerships.

Export Controls and Competitive Implications

Advanced memory technology falls within the scope of export control considerations in several jurisdictions. Depending on Z-Angle Memory's final specifications and manufacturing location, it may be subject to US export control regulations regarding technology transfer to certain countries or end users. This creates potential tensions between commercialization goals (selling globally) and national security concerns.

Competitive implications are also geopolitical. If Z-Angle Memory succeeds, it could break Samsung and SK Hynix's dominance in HBM markets. This outcome would have geopolitical implications, as it would reduce US and other countries' reliance on South Korean suppliers. From South Korea's perspective, Z-Angle Memory represents a competitive threat to strategic industries.

Samsung and SK Hynix dominate the HBM market, controlling approximately 95% combined, leaving only 5% for other competitors. Estimated data.

Alternative Memory Technologies and Competitive Landscape

Emerging Non-Volatile Memory Technologies

Beyond Z-Angle Memory and traditional HBM, several alternative memory approaches are under development. These include emerging non-volatile memory technologies like MRAM (Magnetoresistive RAM), Re RAM (Resistive RAM), and others that potentially offer density advantages. However, these technologies currently don't match HBM's bandwidth characteristics, limiting their applicability for bandwidth-intensive AI workloads.

The memory hierarchy is likely to remain diverse, with different technologies serving different roles. HBM will likely continue dominating high-bandwidth, low-latency applications. Emerging non-volatile technologies may find niches in other applications where density or power efficiency matter more than raw bandwidth.

Photonic and Optical Memory Approaches

Longer-term research explores photonic memory approaches using optical interconnects to replace or augment electrical connections within memory stacks. These approaches could theoretically offer superior power efficiency and bandwidth compared to purely electrical approaches. However, photonic memory remains in early research phases and unlikely to reach commercialization before 2030 or beyond.

Software and Algorithmic Approaches to Memory Pressure

Beyond hardware innovations, software and algorithmic approaches are addressing memory bottlenecks. Techniques like model quantization, knowledge distillation, and sparse model architectures reduce memory requirements without hardware changes. These approaches are complementary to Z-Angle Memory; improved hardware and improved algorithms together will address AI infrastructure bottlenecks.

Financial Viability and Business Model Implications

Capital Requirements for Commercial Success

Transitioning from prototype to commercial production requires massive capital investment. Building or equipping a semiconductor fab capable of advanced memory production costs $5-10 billion or more. Even operating existing fabs at high utilization for Z-Angle Memory production requires capital for equipment, materials, and working capital.

Soft Bank's initial 3 billion yen investment covers prototype development but represents only a small fraction of capital required for commercial production. Successful prototype development would need to be followed by substantially larger investment rounds from Soft Bank, other investors, or Japanese government support mechanisms.

The business model must ultimately generate sufficient returns to justify this capital. If Z-Angle Memory captures even 10-15% of the HBM market by 2032, the company could generate several billion dollars in annual revenue. However, achieving profitability while competing against Samsung and SK Hynix's cost structures remains uncertain.

Competitive Pricing and Market Share Scenarios

Z-Angle Memory's pricing strategy will significantly impact viability. Pricing too high would limit adoption; pricing too low would jeopardize profitability. The optimal strategy likely involves initially pricing 5-10% below Samsung and SK Hynix equivalent products to incentivize adoption, then gradually achieving price parity as volume increases and yield improves.

Market share projections for 2032 might realistically range from 5% (very conservative, minimal adoption) to 20% (aggressive, significant displacement of competitors). At 10% market share in a

Risk-Return Profile for Investors

The risk-return profile for Z-Angle Memory investment is mixed. Potential returns could be substantial if the technology succeeds and captures meaningful market share. However, the risks are equally significant: technical challenges may prove insurmountable, manufacturing yields may not reach acceptable levels, or competitive response from Samsung and SK Hynix may be swift and effective.

For investors, Z-Angle Memory represents a high-risk, high-return venture. This profile is suitable for venture capital or strategic corporate investors (like Soft Bank) rather than traditional capital markets investors seeking stable returns. The success rate for memory startups attempting to disrupt established markets is historically low, which should factor into investment decisions.

Implementation and Adoption Challenges

System Integration and Compatibility

Even if Z-Angle Memory achieves technical specifications, integration into existing AI systems requires careful engineering. GPU and accelerator manufacturers would need to validate Z-Angle Memory compatibility, optimize controllers for the memory interface, and conduct extensive testing. This qualification process typically requires 6-12 months and involves substantial engineering effort.

Backward compatibility with existing HBM infrastructure is unlikely. Z-Angle Memory would require new system designs and potentially new socket or package standards. This limits adoption to new systems and prevents retrofitting existing deployments, reducing the addressable market in the near term.

Customer Risk Aversion and Qualification

Major customers like NVIDIA, AMD, and cloud service providers are risk-averse regarding critical components like memory. A new supplier with limited track record introduces perceived risks around supply continuity, quality consistency, and long-term viability. Overcoming this risk aversion requires demonstrated reliability, long-term contracts, and potentially supply guarantees.

For a company like Saimemory attempting to build trust with conservative enterprise customers, early success stories and reference customers are essential. If early adopters report positive experiences, broader adoption becomes more feasible. If early deployments encounter problems, word spreads quickly and adoption stalls.

Manufacturing Scaling and Supply Reliability

Even assuming Saimemory develops acceptable Z-Angle Memory products, customers will demand supply reliability. Committing to AI infrastructure projects requires confidence that memory supplies will be available throughout the system's lifespan. A new supplier with limited manufacturing experience cannot credibly guarantee this.

Soft Bank and partners must demonstrate manufacturing scale capability and build confidence in supply reliability. Long-term partnerships with established fabs and potentially redundant manufacturing across multiple locations would help build this confidence.

Comparative Technology Assessment

Z-Angle Memory Versus HBM3e

Assuming Z-Angle Memory achieves its claimed specifications, a direct comparison with HBM3e (Samsung and SK Hynix's current flagship product) shows significant potential advantages:

| Specification | HBM3e | Z-Angle Memory (Projected) |

|---|---|---|

| Capacity per Stack | 36 GB | 72-108 GB |

| Bandwidth | 200+ GB/s | 200+ GB/s (assumed) |

| Power per Stack | ~50W (estimated) | ~25W (40-50% reduction) |

| Maturity | Production (2024) | Prototype (2028) |

| Manufacturing Cost | Optimized | Higher initially |

| Availability | Multiple suppliers | Single supplier initially |

These projections reveal Z-Angle Memory's potential advantages and vulnerabilities. Capacity and power advantages are significant. However, HBM3e is mature, available from multiple suppliers, and manufactured at optimized costs. Z-Angle Memory's single-supplier status and higher initial costs represent disadvantages during early production phases.

Z-Angle Memory Versus HBM4

By the time Z-Angle Memory reaches production in 2029, Samsung and SK Hynix will likely have HBM4 products available and ramping. HBM4 is expected to offer superior bandwidth (potentially 400+ GB/s) and continued capacity improvements. The competitive comparison becomes more challenging:

| Factor | Z-Angle (2029) | HBM4 (2029) |

|---|---|---|

| Bandwidth | ~200 GB/s | ~400+ GB/s |

| Capacity | 72-108 GB | ~48-72 GB |

| Power Efficiency | Excellent | Good |

| Market Availability | Limited | Mature, multiple suppliers |

In this scenario, HBM4 offers superior bandwidth but Z-Angle offers superior capacity and power efficiency. Different use cases might prefer different characteristics. This differentiation rather than dominance scenario seems more realistic.

Strategic Alternatives and Contingency Scenarios

Acquisition Scenarios

If Z-Angle Memory development shows promise but commercial path remains uncertain, acquisition could provide an exit strategy for investors. Samsung, SK Hynix, or other memory companies might acquire the technology or the company itself to add to their portfolios or to prevent competition. Intel might acquire deeper involvement if partnership doesn't proceed as planned.

Acquisition would change commercialization trajectory. A Samsung or SK Hynix acquisition would likely integrate Z-Angle Memory into their existing product roadmaps, potentially delaying commercial availability but improving probability of success. An Intel acquisition might accelerate manufacturing in Intel fabs.

Technology Licensing Approach

Instead of manufacturing Z-Angle Memory itself, Saimemory could license the technology to established memory manufacturers. Samsung, SK Hynix, or others might license technology to add to their own roadmaps. This approach would reduce capital requirements and manufacturing risk for Saimemory while providing revenue through licensing fees and royalties.

However, licensing reduces the opportunity to capture premium profits from owning manufacturing. It also requires confidence that licensees will commercialize effectively, which is uncertain for unproven technologies.

Exit From Memory Focus

If Z-Angle Memory development encounters significant technical challenges or if market conditions change, Saimemory could pivot away from memory manufacturing toward other semiconductor segments. The intellectual property might be valuable even if memory manufacturing proves unviable. Alternatively, the project could be abandoned entirely, representing a loss for Soft Bank and Intel but limiting further capital exposure.

Future Trends and Long-Term Implications

Memory Technology Roadmap Beyond 2029

Looking beyond Z-Angle Memory's planned 2029 introduction, memory technology will continue evolving. HBM5 or subsequent generations are likely in development phases. Alternative approaches (3D DRAM, photonic memory, or others) may approach feasibility. The memory landscape of 2035 will likely include multiple competing technologies optimized for different use cases.

Z-Angle Memory's role in this landscape depends on whether it achieves its commercialization targets and customer acceptance. A successful technology could establish Saimemory as a significant player and inspire similar innovations from other companies. Failure would reinforce Samsung and SK Hynix dominance and discourage future disruption attempts.

AI Infrastructure Evolution

AI infrastructure will likely become more specialized and diverse. Rather than a single dominant memory type serving all AI workloads, different memory technologies may optimize for specific use cases. Ultra-fast bandwidth for training, ultra-high capacity for inference, ultra-low power for edge inference—different requirements could drive demand for multiple memory solutions.

Z-Angle Memory's characteristics (high capacity, good power efficiency) align well with inference use cases, where power and cost per inference are primary concerns. This niche specialization could be valuable even if Z-Angle Memory doesn't replace HBM broadly.

Sustainability and Energy Considerations

Energy consumption is increasingly important in data center operations. Z-Angle Memory's claimed power efficiency aligns with broader industry trends toward sustainability. Cloud providers face pressure to reduce energy consumption from shareholders, regulators, and environmental advocates. Technologies that reduce power consumption by 40-50% have significant market value.

This sustainability angle could become increasingly important in Z-Angle Memory's market positioning. Even if performance advantages are modest, power efficiency advantages could justify adoption by environmentally conscious organizations.

Conclusion: Assessing Realistic Success Probability

Balanced Assessment of Opportunities and Risks

Z-Angle Memory represents an intriguing and ambitious initiative that addresses real market opportunities in AI infrastructure. The technology has credible backing from Intel's expertise and Soft Bank's capital. The timing is favorable, with growing AI infrastructure demand expected through 2029 and beyond. The potential advantages—particularly power efficiency and capacity—address genuine pain points for data center operators.

However, significant uncertainties remain. The manufacturing challenges of transitioning from prototype to commercial production are substantial and historically underestimated. Competition from Samsung and SK Hynix's established capabilities and aggressive roadmap advancement is formidable. The historical precedent of technology initiatives like Intel's Optane demonstrates that even well-funded, well-resourced efforts can fail to achieve commercial viability.

The most realistic assessment positions Z-Angle Memory as a meaningful but uncertain endeavor. Success would require flawless execution across prototype development, manufacturing process optimization, cost reduction, customer qualification, and market penetration. Any significant failures in these areas would derail the initiative.

Timeline Realism and Success Metrics

The 2029 commercial availability target is optimistic but not impossible. The 2028 prototype target is more realistic; demonstrating functional prototypes meeting performance specifications is achievable for a well-resourced team. Transition from prototype to commercial production by 2029 remains challenging but possible if no major technical obstacles emerge.

Success metrics beyond timeline include:

- Prototype achievement: Functional samples demonstrating 2-3x capacity and 40-50% power reduction compared to HBM3

- Manufacturing viability: Achieving 50%+ yield in limited production runs

- Cost trajectory: Clear path to cost competitiveness with HBM3e within 2-3 years

- Customer interest: Securing design-in agreements with major system manufacturers

- Volume production: Ramping to millions of units annually by 2031

Meeting all these metrics would position Z-Angle Memory as a success. Meeting some while missing others would result in partial success or failure scenarios.

Strategic Importance for Key Stakeholders

For Intel, Z-Angle Memory success would validate its strategy of diversifying beyond processors into advanced memory and supporting foundry operations. Success would enhance Intel's positioning in AI infrastructure. Even moderate success would strengthen Intel's negotiating position with customers.

For Soft Bank, success would establish the company as a major player in semiconductor technology and fulfill strategic objectives of rebuilding Japanese semiconductor capability. Success would generate significant returns on the modest initial investment and position Soft Bank for larger future opportunities.

For the broader industry, Z-Angle Memory success would break Samsung and SK Hynix's monopolistic position and inject competition into a concentrated market. This competitive pressure would benefit customers through improved pricing and accelerated technology development. It would also encourage other new entrants to pursue memory technology development.

For developers and infrastructure teams, Z-Angle Memory success would provide alternative suppliers and potentially more cost-effective memory solutions, reducing total infrastructure costs. Power efficiency improvements would support sustainability goals. However, qualification and integration work would be required initially.

Key Differentiators Versus Previous Failed Initiatives

Comparing Z-Angle Memory to Intel's Optane and similar failed ventures, several differentiating factors suggest improved probability of success: established market with proven demand (HBM, not a new category), partnership approach rather than going it alone, more modest claims (2-3x, not 10x improvements), involvement of Japanese government industrial policy, and specific focus on energy efficiency as competitive advantage.

These factors don't guarantee success—they merely suggest improved probability relative to previous failures. The semiconductor industry remains brutally competitive, and history judges most disruptive technology claims harshly.

What Success or Failure Would Mean

Z-Angle Memory success (commercial production, customer adoption, market share gains by 2032) would demonstrate that dominant incumbent memory suppliers can be challenged successfully. It would encourage new entrants and inspire alternative technology investments. It would generate billions in value for successful investors. It would improve AI infrastructure availability and reduce costs.

Z-Angle Memory failure (missing timelines, technical problems, insufficient customer adoption) would reinforce the difficulty of disrupting entrenched memory suppliers. It would consume billions in capital with minimal return and potentially discourage future attempts at memory market disruption. It would likely leave Samsung and SK Hynix with even stronger positions through lack of credible competition.

The stakes are substantial in both directions. The next 4-5 years will largely determine which outcome becomes reality as prototype development progresses and commercialization challenges emerge.

Investment Decision Considerations

For investors, Z-Angle Memory presents a high-risk venture capital opportunity. The potential returns justify the risk profile if success probability is adequate. However, the historical failure rate of memory startups and the formidable competitive position of incumbents suggest realistic success probability around 20-30%.

This probability is sufficient for venture capital or strategic corporate investment (where losing multiple investments is expected) but insufficient for conservative investors seeking reliable returns. Soft Bank's portfolio approach, where Z-Angle Memory is one of many technology bets, is appropriate given the risk profile.

For customers and infrastructure teams, Z-Angle Memory should be monitored as a potential future supplier but not depended upon for near-term infrastructure planning. Hedging strategies involving multiple memory suppliers (Samsung, SK Hynix, and future Z-Angle) provide resilience against supply disruptions and pricing pressures from any single supplier.

The Broader Context of Semiconductor Competition

Z-Angle Memory development reflects broader patterns in global semiconductor competition. The US and allies (including Japan) are investing heavily in semiconductor independence and manufacturing capability to reduce reliance on concentrated suppliers and potentially adversarial actors. Memory technology is strategically important because it affects all computing systems, particularly AI infrastructure critical to future economic and military competitiveness.

From this perspective, Z-Angle Memory is valuable not just for its technical merits but for what it represents: a serious attempt to rebuild non-Korean memory supply capacity and establish alternatives to Samsung and SK Hynix dominance. Even if Z-Angle Memory itself fails, the investment validates the importance of memory technology development and may encourage other initiatives.

The semiconductor industry will likely see continued concentration in some sectors (memory, cutting-edge logic) and diversification in others (specialty semiconductors, emerging technologies). Z-Angle Memory's role in this evolving landscape will become clearer as development progresses through 2028 and commercialization approaches.

Ultimately, Z-Angle Memory represents an important but uncertain bet on whether emerging competitors can challenge entrenched memory suppliers. The next 3-4 years will provide substantial evidence about whether this bet will succeed or whether memory market dominance will persist despite substantial challenges and investment. The world of AI infrastructure and those depending on it will benefit significantly if Z-Angle Memory succeeds and faces meaningful consequences if it fails.

FAQ

What is Z-Angle Memory and how does it differ from standard HBM?

Z-Angle Memory is an advanced stacked DRAM architecture being developed by Saimemory (backed by Soft Bank) and Intel, designed to improve upon current high-bandwidth memory (HBM) standards. Unlike traditional HBM designs with vertically stacked layers, Z-Angle Memory uses a tilted or diagonal geometric configuration for memory cells and interconnects, potentially reducing signal path lengths and power consumption by 40-50% while increasing capacity 2-3 times compared to current HBM3 products.

What is the timeline for Z-Angle Memory commercialization?

According to the partnership announcement, functional prototypes are expected by early 2028, with commercial availability targeted for 2029. However, historical precedent suggests timelines for advanced memory technology often experience delays. Volume production and meaningful market penetration would likely extend into 2030-2031, pending successful prototype demonstration and manufacturing optimization.

How much will Z-Angle Memory cost compared to existing HBM products?

No specific pricing details have been disclosed by Intel or Soft Bank. However, initial pricing would likely be competitive with or slightly below Samsung and SK Hynix HBM3e products ($5,000-8,000 per stack) to incentivize adoption. As manufacturing scales and yields improve, costs should decrease toward parity with incumbent suppliers within 2-3 years of commercial launch.

Why is Soft Bank investing in Z-Angle Memory development?

Soft Bank's investment reflects Japan's strategic objective to rebuild domestic semiconductor manufacturing capability and reduce reliance on South Korean memory suppliers. The 3 billion yen investment supports this goal while potentially establishing Soft Bank as a significant player in next-generation memory technology. Success would generate substantial returns and strengthen Soft Bank's position in semiconductor innovation.

What are the major risks that could prevent Z-Angle Memory from succeeding commercially?

Significant risks include: manufacturing yield problems that make production economically unviable, technical challenges in achieving claimed power efficiency and capacity targets, competitive response from Samsung and SK Hynix through accelerated roadmap advancement, supply chain or equipment constraints delaying development, and customer risk aversion limiting adoption despite successful technical development. Historical precedents like Intel's Optane demonstrate that even well-funded initiatives can fail despite technical merit.

How would Z-Angle Memory impact AI data center operations if successfully commercialized?

Successful Z-Angle Memory deployment would provide AI infrastructure operators with multiple benefits: increased memory capacity per stack (supporting larger model deployments), 40-50% power reduction in memory operations (lowering cooling and electricity costs), potential cost advantages through competitive supplier dynamics, and improved sustainability metrics. For a large data center consuming 100+ megawatts, the power savings could translate to $10-15 million in annual operational cost reduction.

Which companies would benefit most from Z-Angle Memory availability?

Cloud service providers running large-scale AI training and inference operations would benefit most, as would GPU/accelerator manufacturers seeking differentiated memory solutions. Companies prioritizing power efficiency and sustainability would find Z-Angle Memory particularly attractive. Initially, companies with flexible supply strategies or those seeking supply diversification away from Samsung and SK Hynix dominance would be early adopters.

What is the likelihood of Z-Angle Memory achieving commercial success by 2032?

Realistic probability assessment suggests 20-30% likelihood of achieving meaningful commercial success (reaching 10%+ market share) by 2032. This reflects historical failure rates of memory technology startups, formidable competition from Samsung and SK Hynix, and substantial manufacturing challenges. While probability is modest, potential returns justify venture capital investment given the high payoff if successful.

How does Z-Angle Memory compare to Samsung and SK Hynix's development roadmaps?

Samsung and SK Hynix are actively developing HBM3e and planning HBM4 products for 2025-2026 timeframes. By 2029, these companies will likely have advanced further, potentially offering superior bandwidth through HBM4. Z-Angle Memory's advantages (capacity, power efficiency) would differentiate rather than dominate compared to flagship HBM4 products, creating opportunity for coexistence rather than replacement of incumbent offerings.

What lessons from Intel's Optane failure apply to Z-Angle Memory development?

Key lessons from Optane's failure include: avoiding overstated performance claims that prove difficult to deliver, ensuring manufacturing economics are viable before scaling, validating customer demand before major capital investment, and maintaining realistic timeline expectations. Z-Angle Memory's more modest claims (2-3x versus Optane's 10x) and partnership approach rather than going it alone represent improvements over Optane's strategy, though execution risks remain substantial.

Could Z-Angle Memory eventually become industry standard like HBM3/HBM3e?

Becoming industry standard would require: achieving technical specifications reliably, securing design-ins with multiple major system manufacturers, demonstrating manufacturing reliability and consistency, achieving cost competitiveness, and building customer confidence through successful deployments. While possible if execution proves flawless, historical precedent suggests likelihood of Z-Angle Memory as one competing option rather than dominating standard remains more probable than replacing HBM as the primary high-bandwidth memory architecture.

Considerations for Runable Integration

While Z-Angle Memory development represents a significant engineering and infrastructure challenge, the broader AI infrastructure landscape it addresses benefits from diverse tools and platforms supporting development. For teams developing AI systems that will eventually deploy on advanced memory infrastructure like Z-Angle Memory, platform choices matter significantly. Organizations building content documentation, technical specifications, and automation workflows around AI infrastructure development benefit from comprehensive solutions that streamline content generation and knowledge management.

Platforms offering AI-powered automation for generating technical documentation, specifications, and reports help engineering teams manage the documentation burden associated with complex projects like Z-Angle Memory integration. As teams evaluate memory technologies and develop infrastructure solutions, having efficient tools for creating architecture documentation, performance comparisons, and deployment specifications accelerates decision-making and implementation.

Key Takeaways

- Z-Angle Memory is an ambitious partnership between Intel and SoftBank targeting commercial availability in 2029 with 2-3x capacity and 40-50% power reduction compared to current HBM3 products

- The technology addresses real market needs for higher-capacity, more power-efficient memory in AI data centers, but faces significant manufacturing and competitive challenges

- Samsung and SK Hynix's dominant market positions and aggressive roadmap advancement pose formidable competition; success probability for Z-Angle Memory estimated at 20-30% by 2032

- Intel's Optane failure and Micron's historical struggles provide cautionary context, though Z-Angle Memory's more modest claims and partnership approach offer improvements over previous disruption attempts

- Manufacturing yield, cost competitiveness, and customer risk aversion represent the most critical success factors; timeline delays are common in advanced memory development

- Successful Z-Angle Memory commercialization would provide AI infrastructure operators with 12-16% total power savings and competitive supplier alternatives in a concentrated market

- The initiative reflects broader geopolitical competition in semiconductors, with Japanese government support aimed at rebuilding domestic memory manufacturing capability and reducing Korean supplier reliance

- Realistic market outcome likely involves Z-Angle Memory as one competing option rather than replacing HBM as industry standard, assuming technical targets are met

Related Articles

- How AI and Nvidia GB10 Hardware Could Eliminate Reporting Roles [2025]

- Intel GPU Development 2025: Strategic Hiring & Nvidia Challenge

- Nvidia's $100B OpenAI Investment: Reality vs. Reports [2025]

- Optical Transistor GPU: How Tulkas T100 Breaks Moore's Law | 2025

- Nvidia's $2B CoreWeave Bet: Vera Rubin CPUs & AI Factories Explained [2025]

- On-Device Contract AI: How SpotDraft's $380M Valuation Changes Enterprise Legal Tech [2025]

![Z-Angle Memory: Intel & SoftBank's HBM Challenge Explained [2025]](https://tryrunable.com/blog/z-angle-memory-intel-softbank-s-hbm-challenge-explained-2025/image-1-1770761264486.png)